|

ソフトウェアエンジニア向けに、Armアーキテクチャをわかりやすく解説するトレーニングコースです。 多岐にわたるArm仕様を短時間で効率的に習得できます。 |

1. トレーニング紹介

2. トレーニングが必要とされる理由

3. 開催スケジュール・お申し込み

eSOLが提供するArmトレーニングの特長

eSOLは正規のArmトレーニングパートナー(ATP)としてArm社より認定を受けており、Armアーキテクチャに関する豊富な経験と知識を持っています。

またeSOLは、リアルタイムOSやデバイスドライバなど下回りのソフトウェア開発経験が豊富で、Arm仕様を熟知しています。多岐にわたるArm仕様のうち、ソフトウェアエンジニアにとって重要な情報は何かを理解しています。

Arm社提供の資料に加え、eSOL独自の補足資料も用い、ソフトウェアエンジニアの視点で分かりやすく説明します。

実例Armv7-Aアーキテクチャソフトウェア開発テクニック – 例外デバッグハンズオンコースでは、実際にデバッガを使用して例外のデバッグ手法を経験できます。

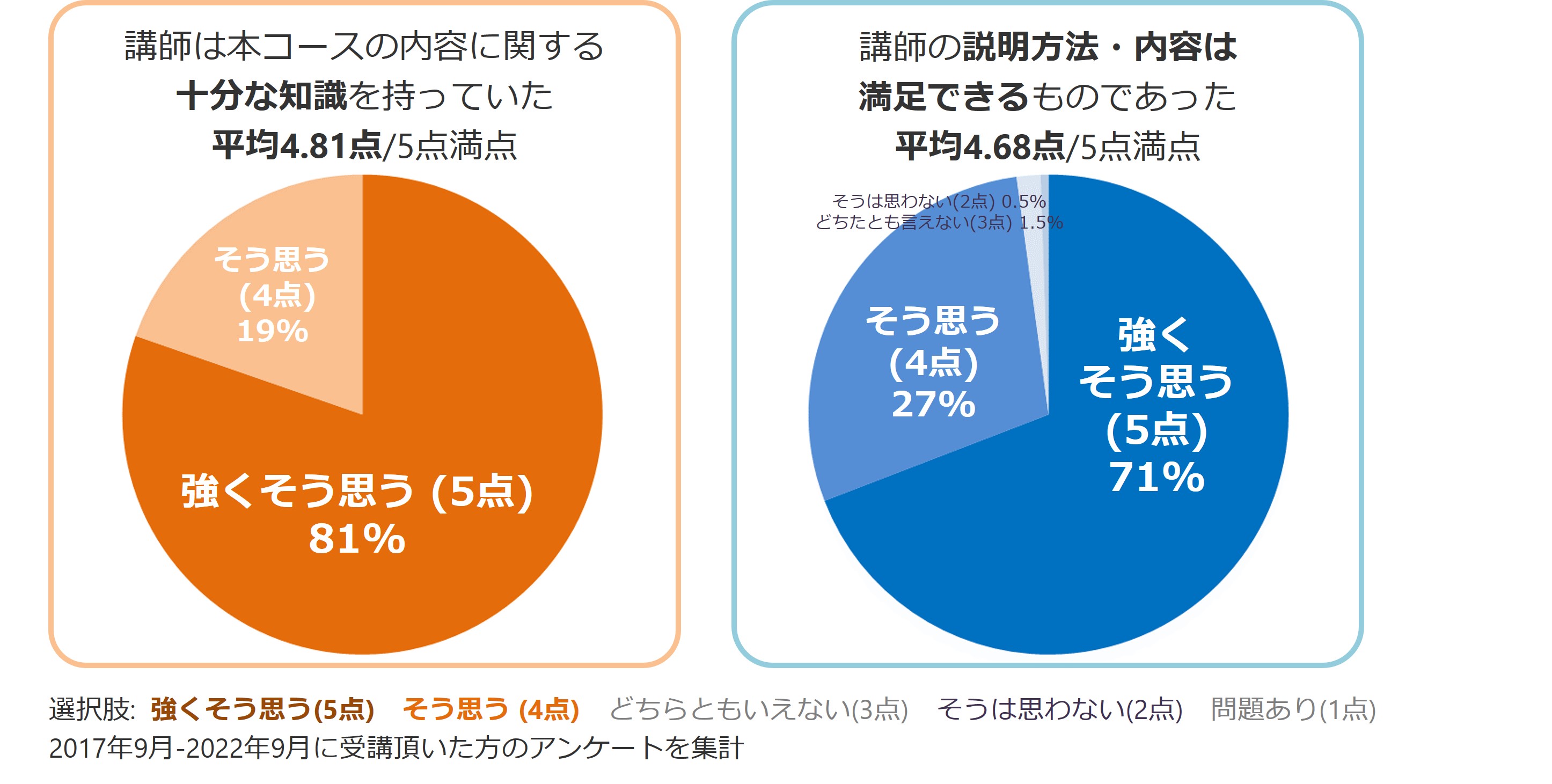

受講者からの高い評価

eSOLのArmトレーニングは、受講者様から高い評価をいただいています。

アプローチの異なる2つのコース+ ハンズオンコース

「広く全体をおさえる」コースと「重要項目をしっかり理解する」コースを提供しています。いずれもArmアーキテクチャのCPUを使って組込みシステムを開発するソフトウェア技術者の方が対象です。

| a) Armアーキテクチャ仕様解説 初めてArmの開発を行うソフトウェア技術者向け |

|

| Armv7-A Cortex-A |

32bit向け | Cortex-A5、Cortex-A7、Cortex-A8、Cortex-A9、Cortex-A15、Cortex-A17 |

| Armv8-A Cortex-A |

64bit(AArch64)向け | Cortex-A32、Cortex-A35、Cortex-A53、Cortex-A55、Cortex-A57、Cortex-A72、Cortex-A73、Cortex-A75 |

| Armv8-R Cortex-R |

32bit(AArch32)向け | Cortex-R52 |

| Armv7-M Cortex-M |

32bit向け | Cortex-M0、Cortex-M0+、Cortex-M3、Cortex-M4、Cortex-M7 |

- Arm社より提供されたテキストに沿って、Armアーキテクチャの全体像を解説

- 特に難しいポイントはeSOLオリジナルの補足資料も使用し、 2日間で効率よく説明

トレーニング内容

| 例)Armv7-Aコース | |

| 1日目 | 2日目 |

|

1. Armアーキテクチャ概要 2. Armv7-Aアセンブラ命令概要 3. メモリ管理とMMU 4. 例外処理と割り込み、GIC概要 |

5. キャッシュと分岐予測 6. メモリバリア 7. マルチコア環境におけるキャッシュ管理・共用メモリの扱い 8. スタンバイモード |

| 例)Armv7-Mコース | |

| 1日目 | 2日目 |

|

1. Armアーキテクチャ概要 2. Cortex-M3、M4とM7概要 3. Armv7-Mアセンブラ命令概要 4. 例外処理と割り込み |

5. メモリ属性 6. メモリバリア 7. MPU 8. マルチコア環境におけるキャッシュ管理・共用メモリの扱い |

受講者様からいただいた感想

- 自力で学習するよりも、はるかに短時間で効率よくArmアーキテクチャを理解できた。

- Armを初めて使う前に、注意すべき点やアーキテクチャの動作を知るのに良い内容だった。

- 説明が丁寧で判りやすかった。

- Arm社テキストのほか、詳細を説明するオリジナル資料があり、良かった。

|

b) 実例Armアーキテクチャソフトウェア開発テクニック Armを使っているが、まだ理解が浅いと感じている若手~中堅エンジニア向け |

|

| Armv7-A Cortex-A |

32bit向け | Cortex-A5、Cortex-A7、Cortex-A8、Cortex-A9、Cortex-A15、Cortex-A17 |

| Armv8-A Cortex-A |

64bit(AArch64)向け | Cortex-A32、Cortex-A35、Cortex-A53、Cortex-A55、Cortex-A57、Cortex-A72、Cortex-A73、Cortex-A75 |

Armアーキテクチャ上での豊富な開発経験をもとにeSOLで抽出した、特に重要な以下の2つのテーマを中心に解説します。

1) 発生した例外の原因を独力で解析できる

2) メモリオーダリングやキャッシュの特性を踏まえて適切にドライバを実装できる・バリアの使い方を理解できる

eSOLオリジナルテキストと演習を通じて詳細に解説します。

- Arm仕様を具体的にはどのようにプログラムに適用すれば良いのか

- 不具合を作り込みやすいポイントと回避する方法

- 予期せぬ例外が発生してしまった時の解析ポイント

トレーニング内容

| 1日目 | 2日目 |

|

1. Armアーキテクチャ概要 2. Armアセンブラ命令概要 (v7-A または v8-A AArch64) 演習:アセンブラ 演習:AAPCS(関数呼び出し標準) 3. メモリモデルとキャッシュ・バリア・投機実行 演習:メモリモデル・キャッシュ・バリア |

4. 例外ハンドリング 演習:例外発生箇所の見つけ方 演習:逆アセンブルリストとCプログラムとの対応 演習:例外のデバッグ手法 5. 組込みシステムでCソースを記述する際の留意点 |

受講者様からいただいた感想

- 概要だけでなく実例・経験を交えた例題や説明がされているので役に立ちました。

- Armアーキテクチャ特有の制約について、実際にはまりそうな内容の説明があり、有益でした。

- 実用的な内容になっており開発につながりやすいと思いました。

- 演習で理解が深まりました。

- バリア、バッファ周りの振る舞いを理解できました。

- スタックからのトレースの方法が有益でした。

※Armv8-A, Armv7-A/Rでは、a)「アーキテクチャ仕様解説」2日間とb)「実例ソフトウェア開発テクニック」2日間の内容をあわせて3日間で受講することが可能です。時間と費用を節約できます。

|

c) 実例Armv7-Aアーキテクチャソフトウェア開発テクニック -例外デバッグ ハンズオンコース Armを使っているが、まだ理解が浅いと感じている 若手~中堅エンジニア向け 例外発生時のデバッグ手法を身に付けたい方 |

|

| Armv7-A Cortex-A |

32bit向け | Cortex-A5、Cortex-A7、Cortex-A8、Cortex-A9、Cortex-A15、Cortex-A17 |

「b) 実例Armアーキテクチャソフトウェア開発テクニック」にて解説しているテーマの1つ、「1) 発生した例外の原因を独力で解析できる」に関して、デバッガ(IDE)を1人1台使用し、実際にデバッグを行います。

eSOLオリジナルテキストを用い、デバッグの方針・勘所を講師が丁寧に説明しますので例外デバッグ未経験者でもデバッグ手法を身に付けることが出来ます。少人数クラス(最大5名)ですので実習中、講師に気軽に質問し理解を深めることが出来ます。

トレーニング内容

| 1日コース |

|

関連動画

|

|

関連資料

オンライン無料相談会もご利用ください。

Zoomなどのオンライン会議ツールで行える無料相談会を実施しています。弊社社員と時間を設けて会話しながら相談したい、という場合は、ぜひこちらをご活用ください。